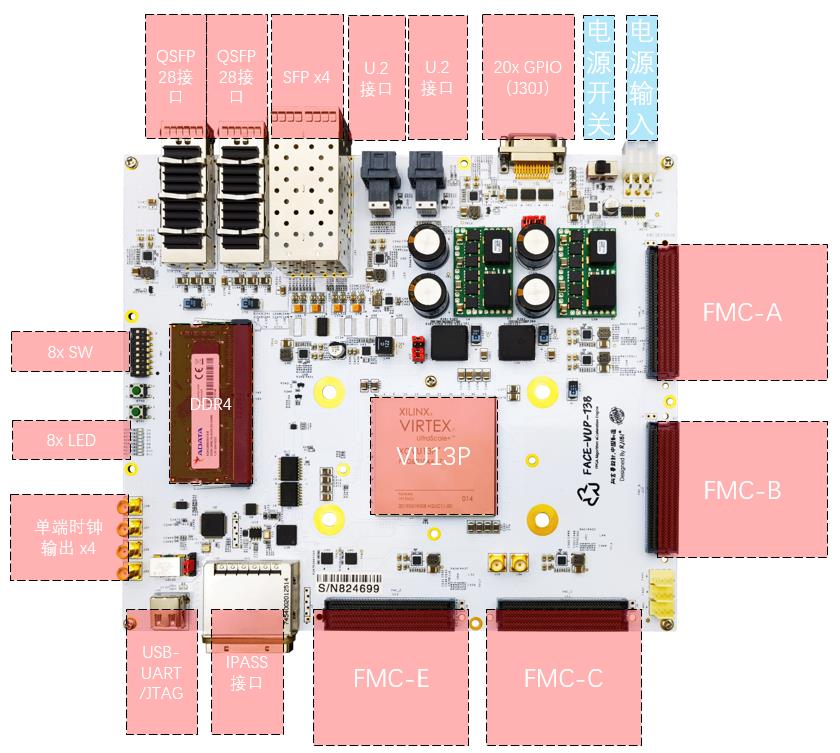

FACE-VUP-13B

大规模原型验证平台

特点

✦ Virtex UltraScale+ XCVU13P-2FHGB2104I(可选XCVU9P-2FLGB2104I)

✦ 8GB DDR4 SODIMM x1

✦ 配置存储:Dual QSPI Flash

✦ SFP+接口 x4

✦ QSFP28 x2

✦ USB-UART

✦ PCIe Gen3x8

✦ U.2 NVMe SSD x2

✦ FMC-HPC (LA+HA+HB+8GT)x1

✦ FMC-HPC (LA+HA+8GT)x1

✦ FMC-HPC(LA+8GT)x2

✦ 板载10路可配置时钟源SI5345

✦ 板载100M高精度时钟源

✦ 板载时钟输出BUFFER

概述

FACE(FPGA Algorithm aCceleration Engine)FPGA算法加速开发引擎是基于FPGA可编程器件构建的一系列算法加速开发引擎平台。其旨在通过借助FPG丰富的可编程资源、并行算法实现搭配外围大容量DDR3/DDR4存储以及PCIe、QSFP、SATA等高速接口,助力高校和科研院所相关科研项目的算法开发与部署。

FACE-VUP-13B大规模FPGA原型验证平台是FACE系列的最新产品。FACE-VUP搭载16nm工艺的Virtex UltraScale+系列主器件。XCVU13P主器件具有极其丰富的FPGA可编程逻辑资源,提供了强悍的算法原型验证能力。该平台提供有丰富计算资源的同时还具备有非常丰富的外设接口:SFP+、QSFP28、IPASS PCIe、FMC等;非常适用于ASIC原型验证,高性能计算系统原型开发等场景。

框图

主要规格

FACE-VUP-13B平台

搭载FPGA主器件为:XCVU13P-2FHGB2104I(可选XCVU5P-2FLVB2104I或XCVU7P-2FLVB2104I或XCVU9P-2FLGB2104I或XCVU11P-2FLGB2104I)

板卡主要外设

✦ DDR4 SODIMM插槽,搭载8GB DDR4 内存条

✦ USB-UART接口

✦ USB-JTAG配置接口

✦ Dual QSPI Flash 存储器

✦ PCIe Gen3x8接口

✦ QSFP28接口2个

✦ SFP+ 接口4个

✦ FMC-HPC连接器4个

✦ U.2 NVMe SSD 2个

资源图

实物资源图如下:

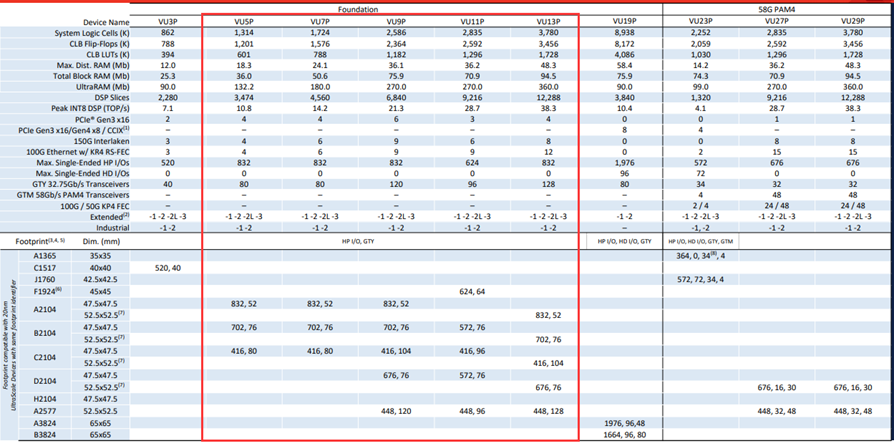

芯片资源

✦ XCVU13P-2FHGB2104I,其资源如下:

✦ 逻辑资源3,780,000 Logic Cells

✦ 触发器数量3,456,000

✦ BRAM存储容量94.5Mb

✦ DSP核心数量12,288个

✦ 高速串行收发器GTY(32.75Gb/s Max Rate)76个

✦ 用户可用IO数量702

主要参考设计

✦ IBERT测试工程

✦ DDR4测试工程

✦ PCIe Gen3 x8 测试工程

✦ FMC回环测试工程

✦ SI5345时钟配置工程

冷却

✦ 标准:主动散热

功率

✦ 板载大功率电源 up to 100W

板卡外形

✦ 通用版型