FACE-RFSoC-B

8发8收射频开发平台

特点

资料整理中

概述

FACE(FPGA Algorithm aCceleration Engine)FPGA算法加速开发引擎是基于FPGA可编程器件构建的一系列算法加速开发引擎平台。其旨在通过借助FPGA与ARM灵活的软硬件全可编程能力、并行算法实现以及动态可重构的特性搭配外围大容量DDR3/DDR4存储以及PCIe、QSFP、SATA等高速接口,助力高校和科研院所相关科研项目的算法开发与部署。

FACE-ZU-15EG是FACE系列中的一员,FACE-ZU平台同时搭载16nm工艺的ZYNQ UltraScale器件以及28nm的ZYNQ-7000全可编程器件。

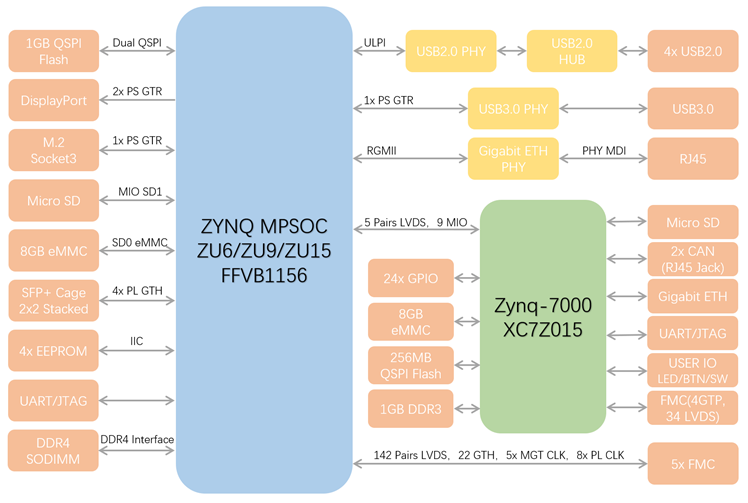

框图

主要规格

FACE-ZU平台

✦ 搭载FPGA主器件为:XCZU15EG-2FFVB1156I

✦ 板载FPGA协处理器件为:XC7Z015-2CLG485I

板卡主要外设

✦ PS DDR4 SODIMM插槽,搭载8GB DDR4 2400Mhz内存条

✦ PS 千兆以太网

✦ PS USB 3.0接口

✦ PS USB 2.0 x4 接口

✦ PS EMMC 8GB存储器

✦ PS QSPI Flash 512MB存储器

✦ PS Micro-SD卡槽

✦ PS USB-UART接口

✦ PS USB-JTAG接口

✦ PS PCIe(M.2)接口

✦ PL SFP+ 4个光接口

✦ PL FMC扩展连接器 5个

✦ FMC-A:4对GTH,6对LVDS, 1个GTH时钟

✦ FMC-B:4对GTH,34对LVDS,2个PL差分时钟,1个GTH时钟

✦ FMC-C:4对GTH,34对LVDS,2个PL差分时钟,1个GTH时钟

✦ FMC-D:4对GTH,34对LVDS,2个PL差分时钟,1个GTH时钟

✦ FMC-E:4对GTH,34对LVDS,2个PL差分时钟,1个GTH时钟

ZYNQ协处理器外设

✦ PS部分

✦ PS DDR3 1024MB存储器

✦ PS QSPI Flash 256MB存储器

✦ PS 千兆以太网

✦ PS EMMC 8GB存储器

✦ PS Micro-SD卡槽

✦ PS CAN接口2个

✦ PS USB-UART接口

✦ PS USB-JTAG接口

✦ PL部分

✦ PL FMC扩展连接器1个(4对GTP,34对LVDS,2个PL差分时钟,1个MGT时钟)

✦ PL LED灯 x4

✦ PL 按键 x2

✦ PL 开关 x4

✦ PL 排针扩展IO x24

✦ PL端提供5对LVDS信号与ZYNQ MPSoC PL互联,9根单端信号与ZYNQ MPSoC PS MIO互连

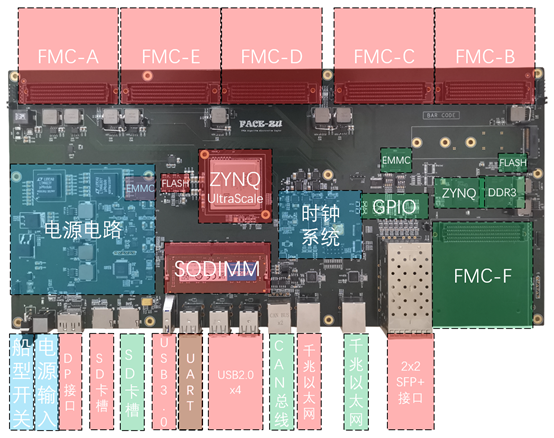

资源图

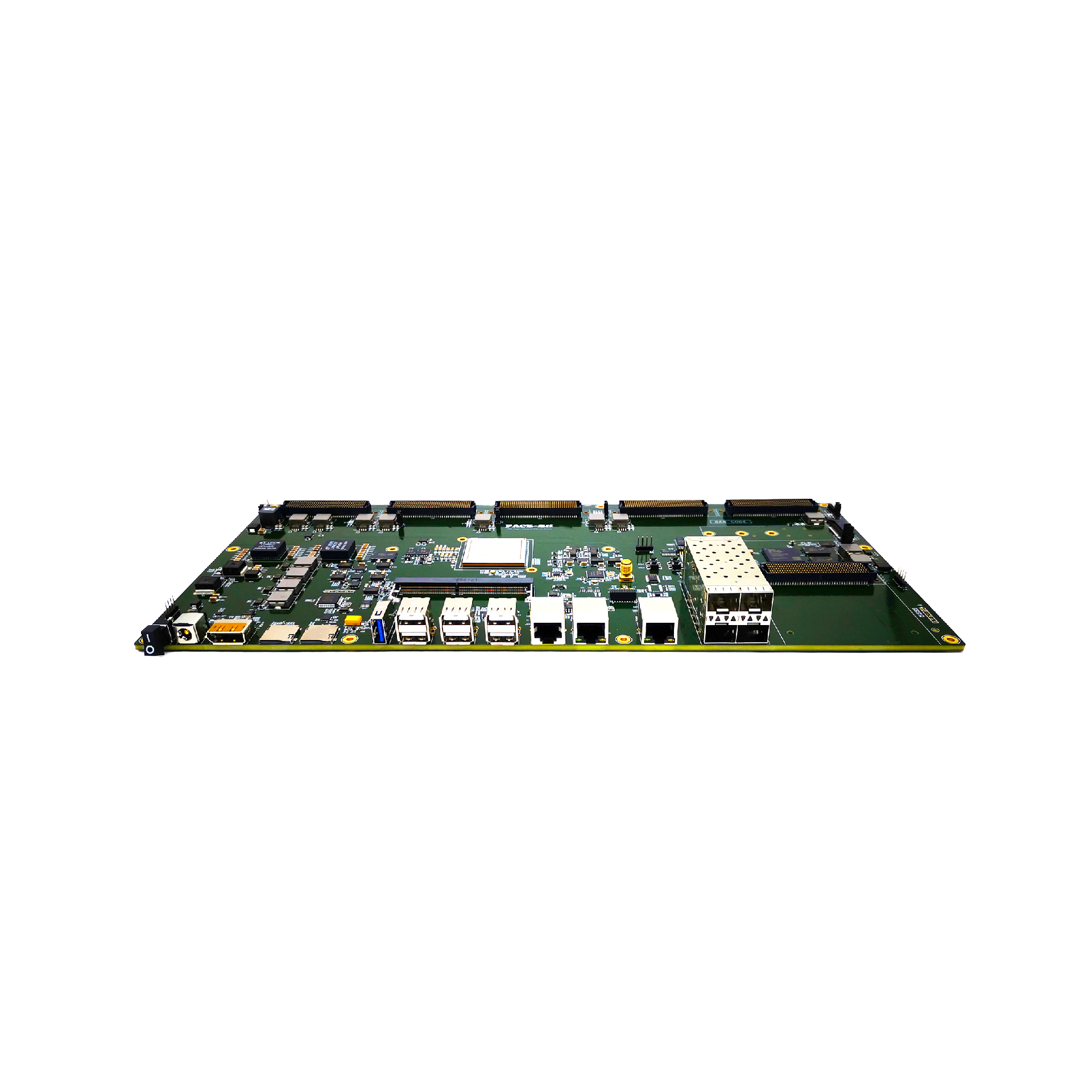

实物资源图如下:

平台详述

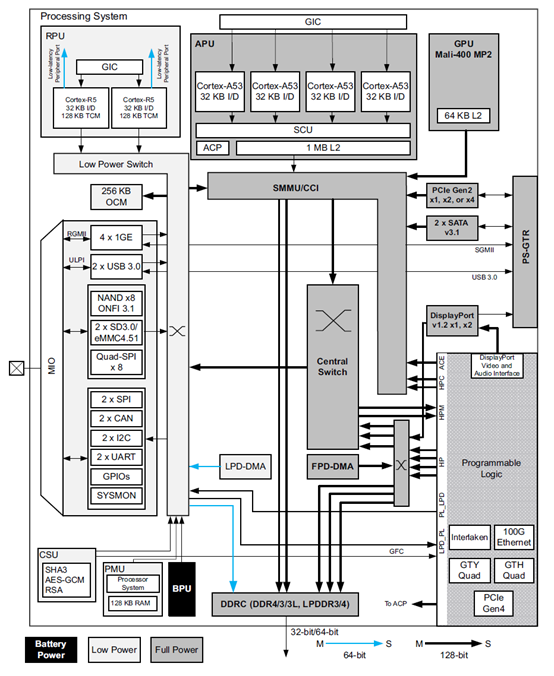

✦ Zynq UltraScale+ MPSoC处理器系统具有三个主要的处理单元:

✦ Cortex-A53应用程序处理单元(APU)——基于Arm v8架构的64位四核CPU

✦ Cortex-R5实时处理单元(RPU)——基于Arm v7架构的32位双实时处理单元,带有专用的紧密耦合存储器(TCM)

✦ ARM Mali™-400 MP2(GPU)——带有像素和几何处理器以及64 KB L2缓存的图形处理单元

✦ Zynq UltraScale+ MPSoC处理器系统具有四个高速串行I/O(HSSIO)接口,并支持多种高速接口协议:

✦ 符合PCI Express 2.1规范的集成块

✦ SATA 3.1接口

✦ DisplayPort接口,可支持4Kx2K分辨率

✦ USB3.0接口,支持5Gb/s线速率

✦ 串行GMII接口,支持1Gb/s速率

ZYNQ MPSoC框图

主要参考设计

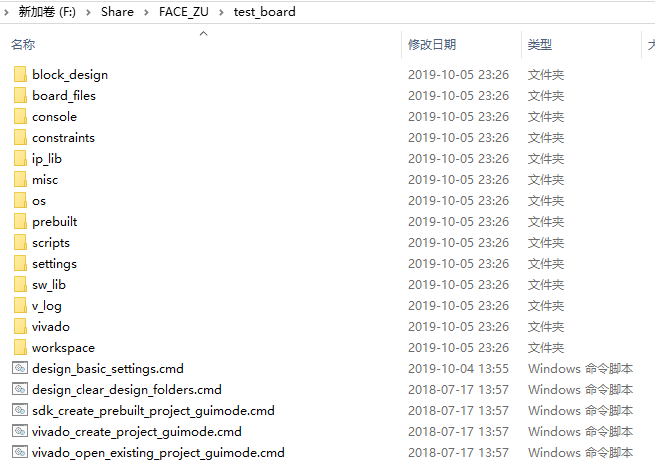

✦ TE开发框架

✦ 支持一键创建Vivado设计

✦ 支持一键打开工程

✦ 支持一键编译HSI软件工程

✦ 支持一键生成配置文件

开发环境

✦ 开发框架安装

✦ 解压框架安装包至PC目录

✦ Vivado开发环境安装

✦ 安装Vivado 2018.2 系统版本

✦ PetaLinux开发环境安装

✦ 安装PetaLinux 2018.2版本

✦ 需Linux OS下安装,推荐Ubuntu16.04版本

冷却

✦ 标准:主动散热

电源

✦ 板载大功率电源,24V直流

板卡外形

✦ 通用版型